一种“绝端”条件下的输入测试(续1)

2)S7-1214C测试:连接好I0.0的外部输入及plc24V电源经过3P断路器。

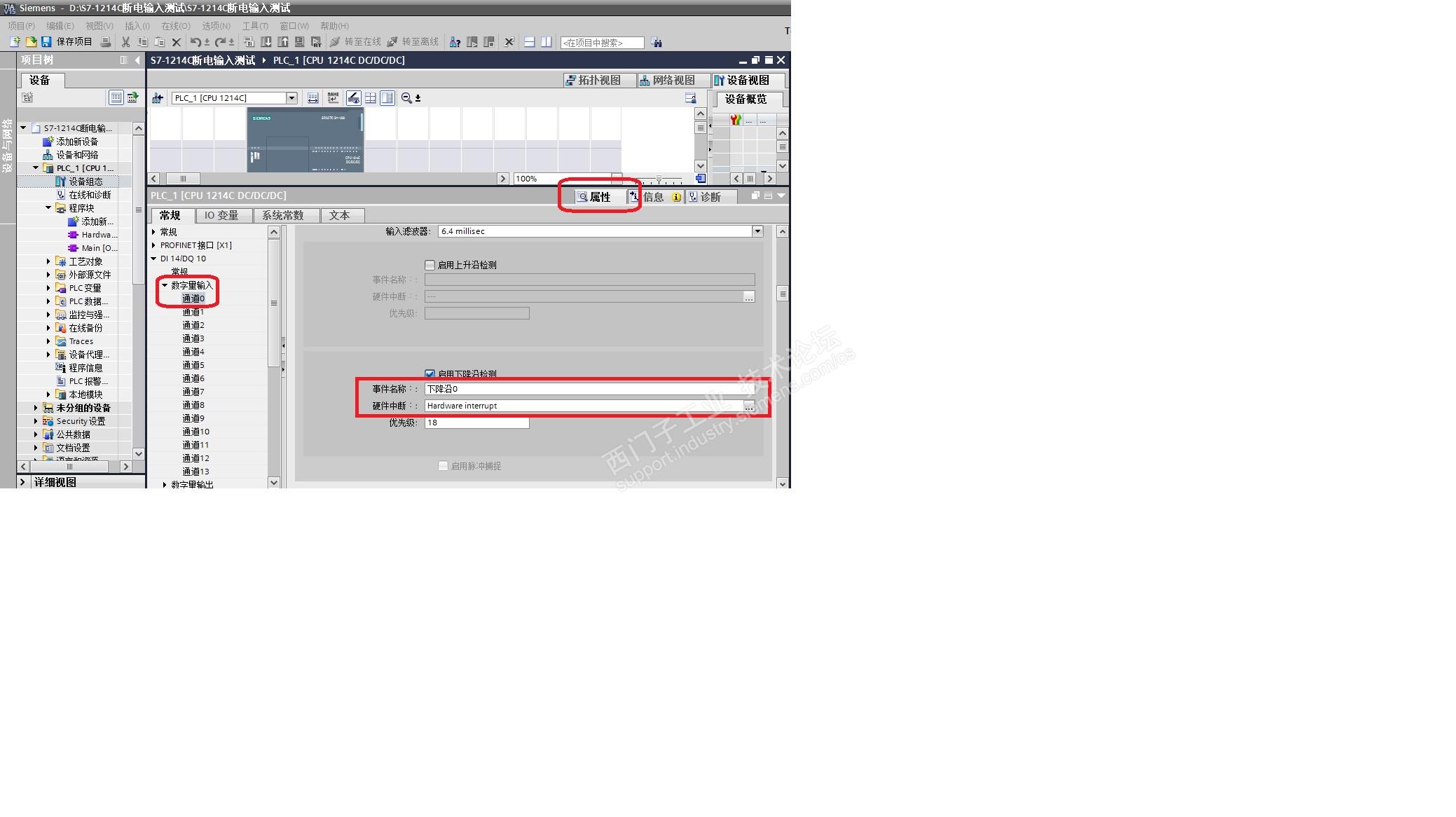

创建一个新项目,选择cpu为S7-1214C DC/DC/DC,在cpu属性中“数字量输入通道0”选择“下降沿中断”,并关联一个外部输入下降沿中断组织块OB40:

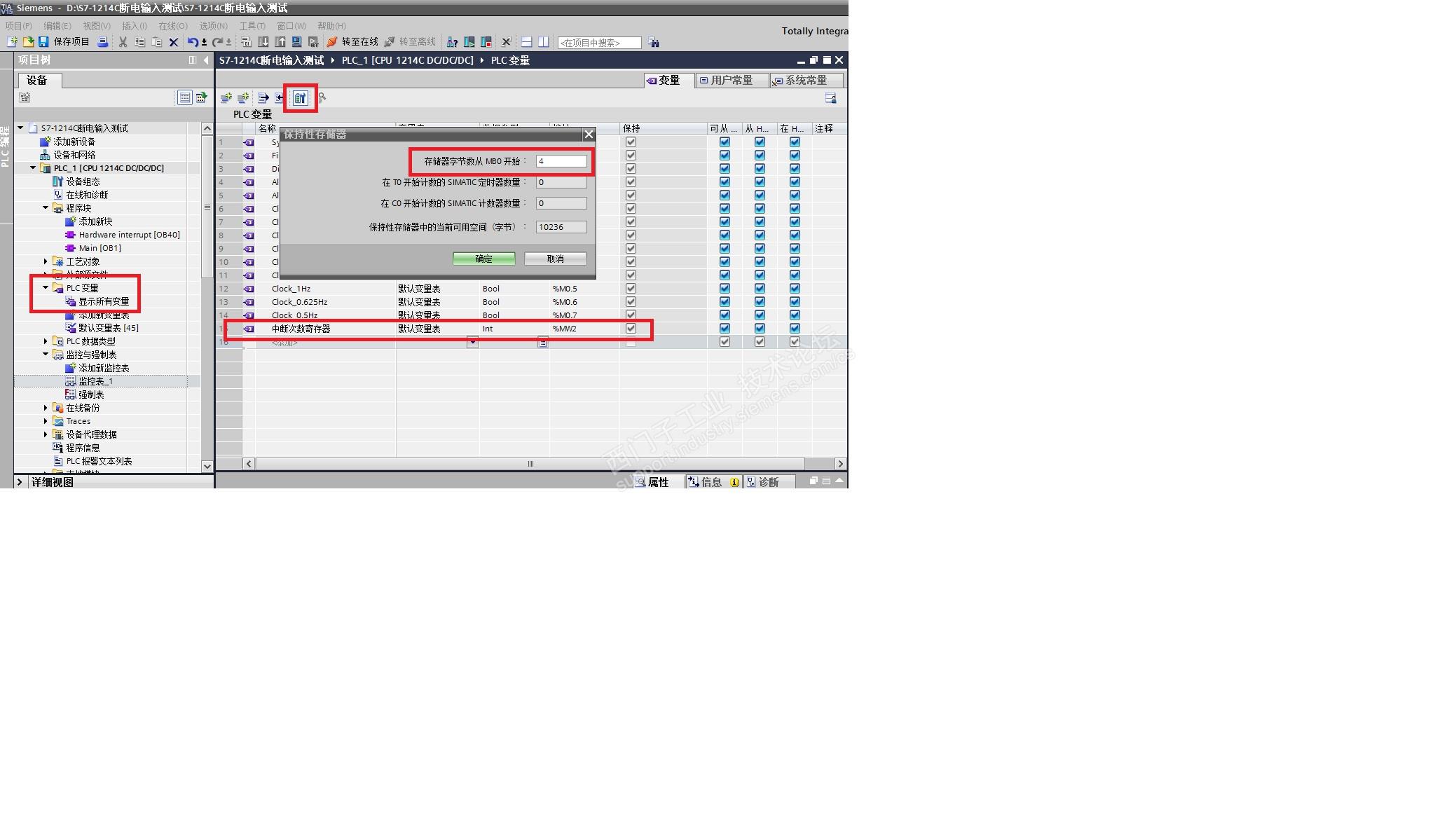

选择“系统和时钟存储器”,地址默认。

创建中断次数存储所需要的变量MW2,并设置为断电保持性地址区:

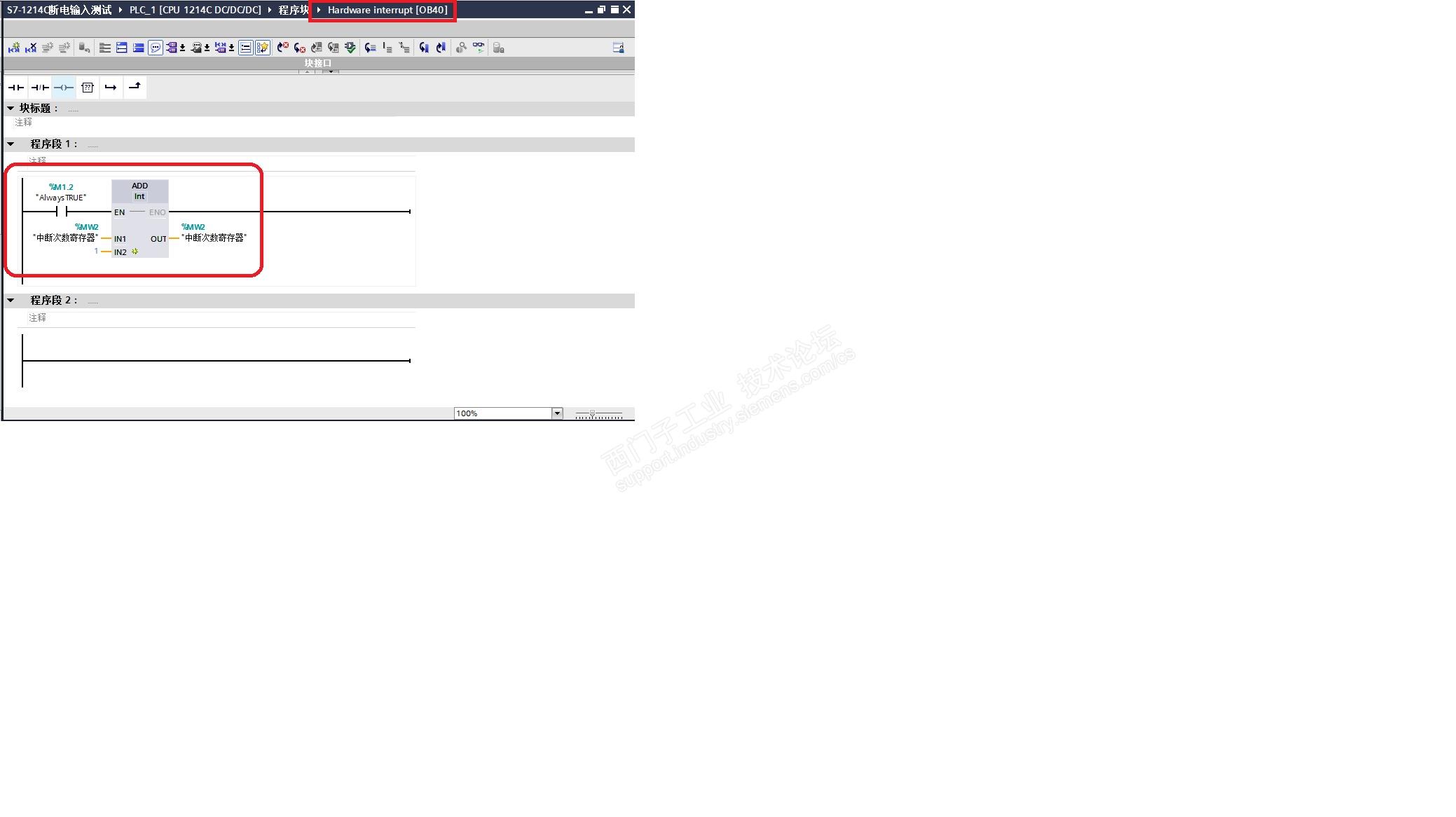

在OB40中编辑,中断次数累加程序:

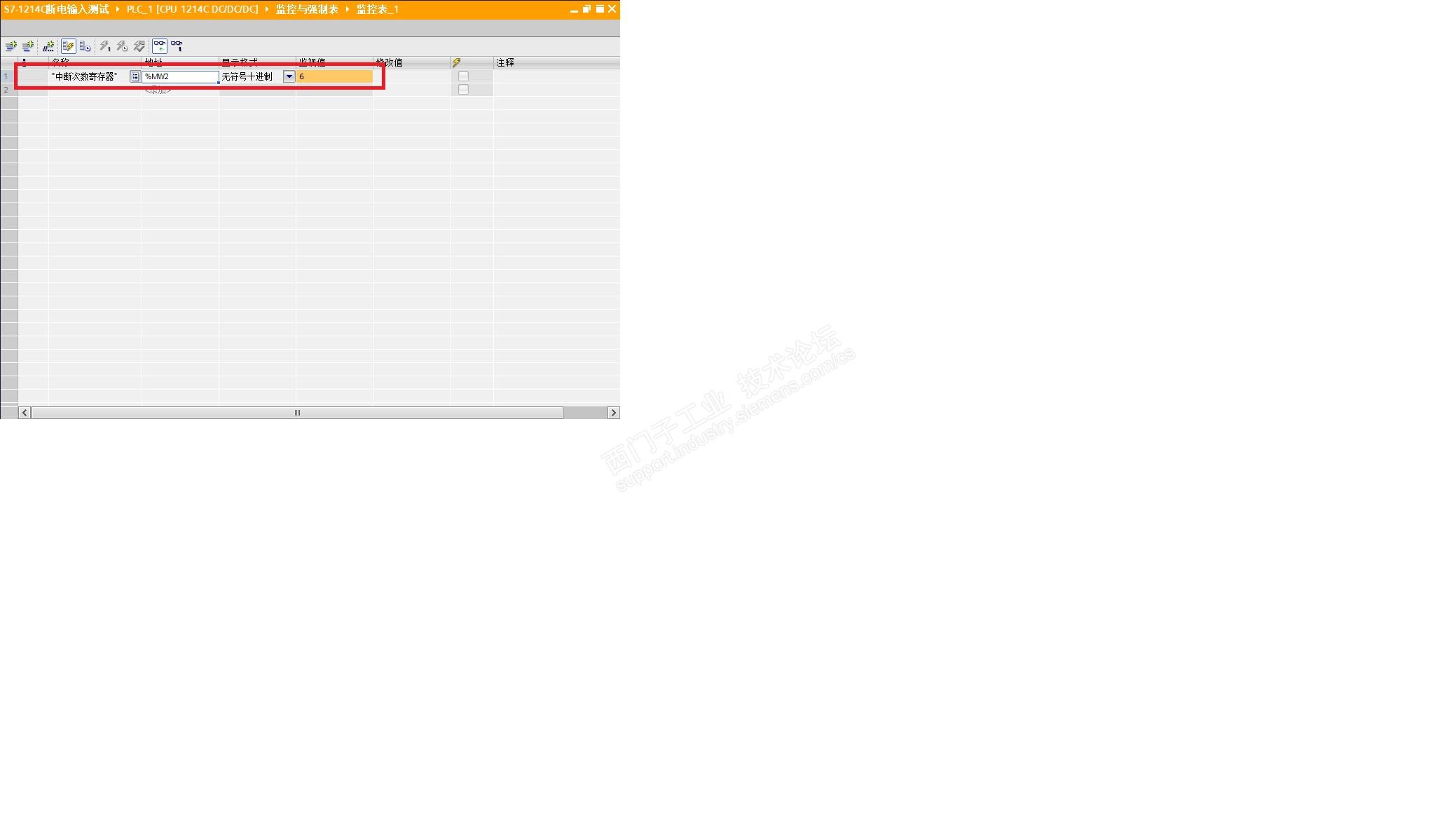

程序编译、保存后下载,再创建一个监控表,看MW2数据:

通、断了6次,每次均能够顺利记录。